# **Preliminary Data Brief**

2020/4/13 V1.3

# S5KM312C

**Smart mmWave Sensor Series**

## **S5KM312C**

#### 1 Device Overview

#### 1.1 Main Features

- 24GHz K-band highly integrated FMCW radar sensor SoC

- Up to 4GHz bandwidth FM tuning range

- Integrated one transmitter channel and two receiver channels

- Integrated FM signal generator and low phase noise PLL

- · On-chip 16bits ADCs in the receiver baseband

- On-chip hardware accelerator for digital signal processing

- · Support multi-chip cascade application

### 1.2 Applications

Motion detection

• TX maximum output power: 12dBm

• RX noise figure: 10.5dB

• PLL phase noise: -97dBc @ 1MHz offset

• Command IIC/SPI/UART for chip configuration

· Data SPI/UART for serialized data output

· Single power supply voltage 3.3V

4 x 4 mm<sup>2</sup> QFN32 package

Range / velocity / angle measurement

Vital signs monitoring

Figure 1. Smart mmWave Sensor's Application

#### 1.3 General Description

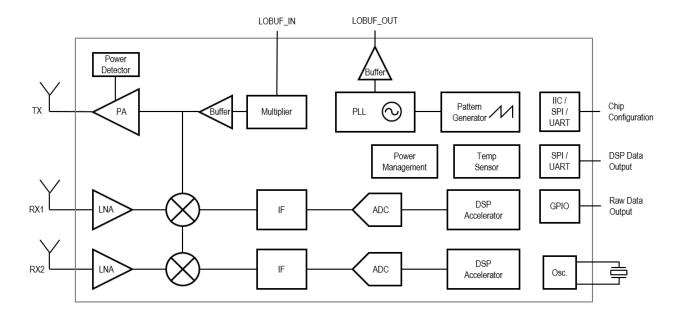

Figure 2. S5KM312C Diagram

The S5KM312C is a highly integrated SoC mmWave sensor which is used to provide a compact solution for radar sensor system. Based on FMCW radar technology, it is capable of operation at 24GHz K-band with up to 4GHz continuous chirp.

The device includes a fully on-chip K-band RF transceiver, driven by on-chip pattern generator and PLL. The pattern generator can support several frequency sweep modes that generate various waveforms in the frequency domain, for example, saw-tooth and triangular waveforms. Additionally, a local buffer system is available for multi-chip cascade applications. The generator and PLL support fast chirp mode.

The RF and Analog subsystem contain one transmitter (TX) and two receivers (RX1 and RX2). Gain controls are applied to both transmitter and receivers to adjust the whole link budget to work in different scenarios. In the receivers, it integrates IQ basebands including inter-mediate frequency (IF) amplifiers, filters and ADCs. DSP accelerators are followed by the ADCs, which run data processing such as the FFT of the IQ ADCs' outputs. The processed data can be output in serialized manner through flex output pins via SPI or UART.

The S5KM312C requires minimum external components i.e. the external crystal oscillator and stabilization capacitors as the high level of integration. It can be operated with a single power supply at 3.3V thanks to the internal power management engine, and the device is fully configurable via IIC/SPI/UART.

## 2 Main Performance

Table 1. Main Parameters

| Parameter             | Description               | Min  | Тур  | Max  | Units | Condition                                                                                             |

|-----------------------|---------------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------|

| Vcc                   | Supply voltage            | 3.0  | 3.3  | 3.6  | V     |                                                                                                       |

| Icc                   | Current consumption       |      | 79   |      | mA    | all the circuits work at default setting mode and all the circuits are on, with 50% duty cycle chirp. |

| F_Out                 | TX output frequency range | 22.5 |      | 27.5 | GHz   | 3dB bandwidth                                                                                         |

| P <sub>max</sub> _Out | TX maximum output power   |      | 12   |      | dBm   |                                                                                                       |

| F_In                  | RX input frequency range  | 22.5 |      | 27.5 | GHz   | 3dB bandwidth                                                                                         |

| NF                    | RX noise figure           |      | 10.5 |      | dB    | including RF, analog and ADC                                                                          |

| G_RX_RF               | gain of LNA + Mixer in RX | 15   |      | 31   | dB    |                                                                                                       |

| BW_Chirp              | FMCW chirp bandwidth      |      |      | 4    | GHz   |                                                                                                       |

| PN                    | Phase noise of PLL        |      | -97  |      | dBc   | phase noise at 1MHz offset                                                                            |

| Res_ADC               | ADC resolution            |      | 16   |      | bits  |                                                                                                       |

| Fs                    | ADC sampling frequency    |      | 2.5  |      | MHz   |                                                                                                       |

## **3 Revision History**

Table 2. Document Revision History

| Date       | Revision | Author               | Changes                                           |

|------------|----------|----------------------|---------------------------------------------------|

| 2019/12/10 | V1.0     | Marketing Department | Initial Release                                   |

| 2020/3/3   | V1.1     | Marketing Department | Update F_in、F_out、NF、PN performance、Add           |

|            |          |                      | R_RX_RF、Fs performance                            |

| 2020/3/31  | V1.2     | Marketing Department | Update block diagram、description, and F_in、F_out、 |

|            |          |                      | performance                                       |

| 2020/4/13  | V1.3     | Marketing Department | Update Icc and G_RX_RF                            |